【技术分享】FPGA杂记之基础篇二及Demo案例

发布时间2021-01-19

分享

前言

本文接续上一篇《FPGA杂记基础篇》,继续为大家分享IP例化和几个基于FPGA芯片实现的Demo工程。

IP例化

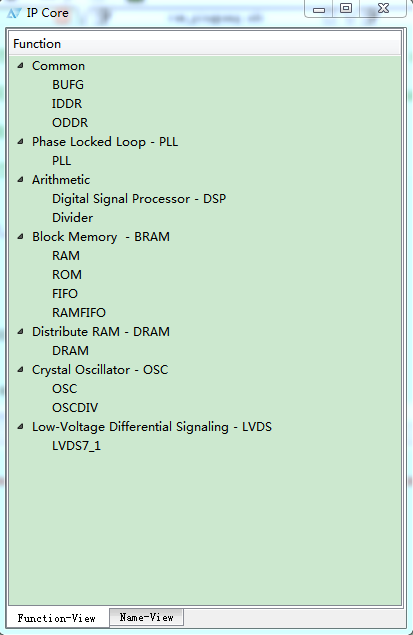

IP即是一个封装好的模块,集成在相应的开发环境里面,以亚星官网的TD软件为例,不同系列的芯片集成了不同的IP模块,可以通过软件例化调用。

以下是亚星官网TD4.6.5集成的EF3L40CG332B的相关IP。

1.1 PLL&RAM

以例化PLL和RAM为例,实现两个异步双口 RAM。

读写时钟都设置 100Mhz, 两个 RAM 为 RAMA 和RAMB, 深度为 1024,位宽为 8bit,写入数据为 8bit,100Mhz 持续数据流, 当 RAMA被写入 1024 字节数据后切换到写 RAMB, RAMB 被写入 1024 字节后切换 RAMA。以此循环类推。

当 RAMA 被写入 1024 字节时, 给读时序提供一个启动信号读取 RAMA 的数据, 读取完 RAMA 的 1024 字节数据时, 切换读 RAMB 以此类推。

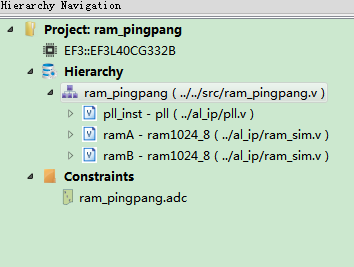

这个工程的工程结构如下图:

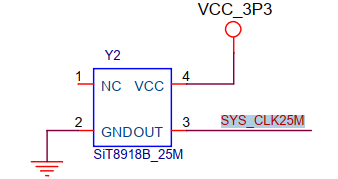

首先EF3L40CG332B_DEV开发板提供了25Mhz的晶振时钟输入到EF3L40CG332B的时钟管脚。

想要得到100Mhz的读写速率,需要先用PLL得到倍频时钟。

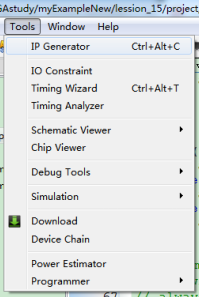

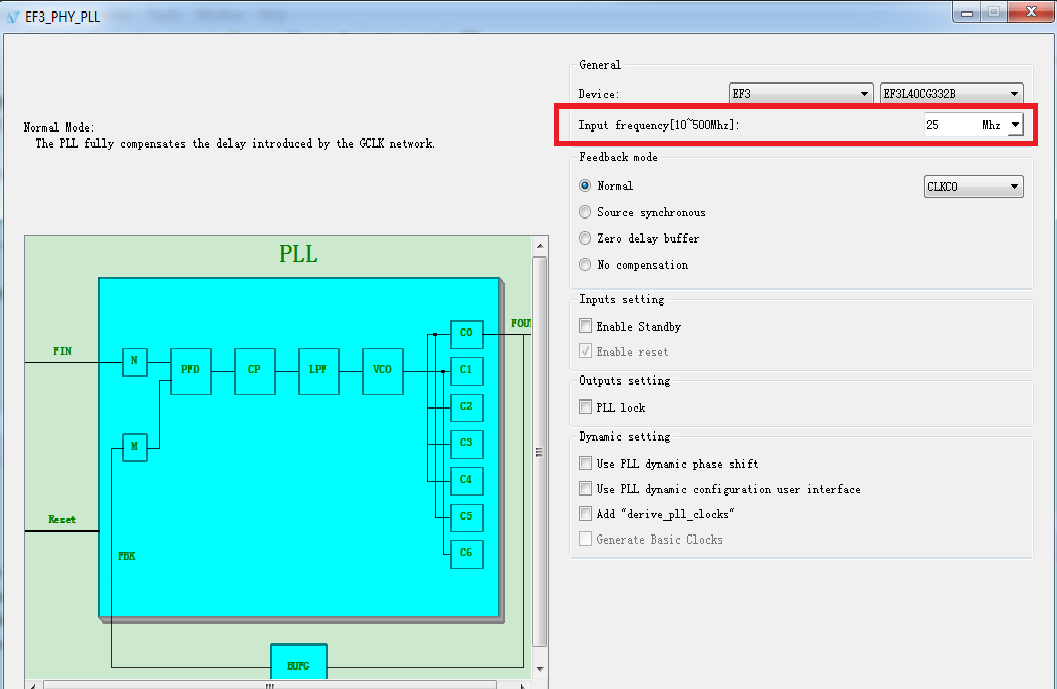

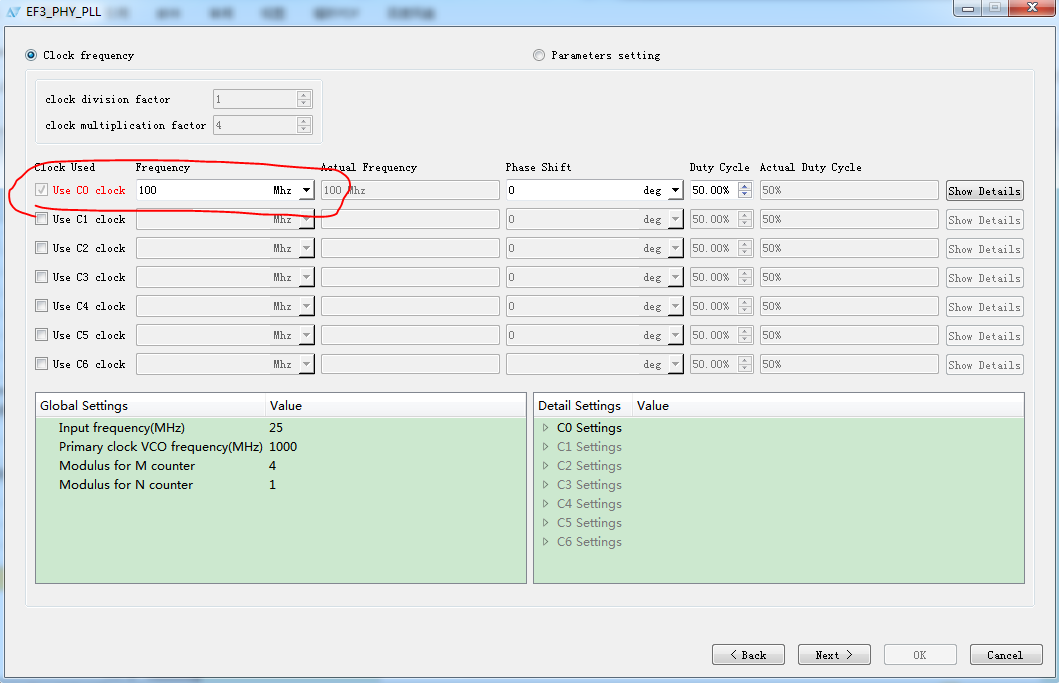

在tools目录下点击IP Generator进入IP core页面,并选择PLL,输入时钟填入板子晶振25Mhz。

输出时钟填入所需要的100Mhz,并从C0输出。

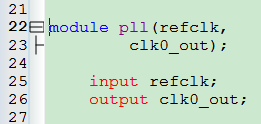

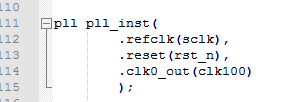

设置完成后,生成的module声明如下(完整模块可参考代码)

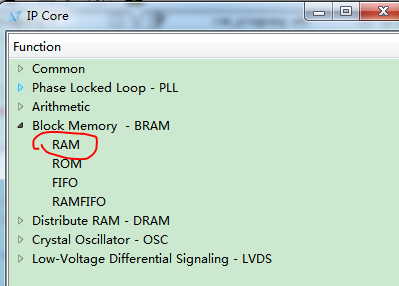

再生成ram的IP模块

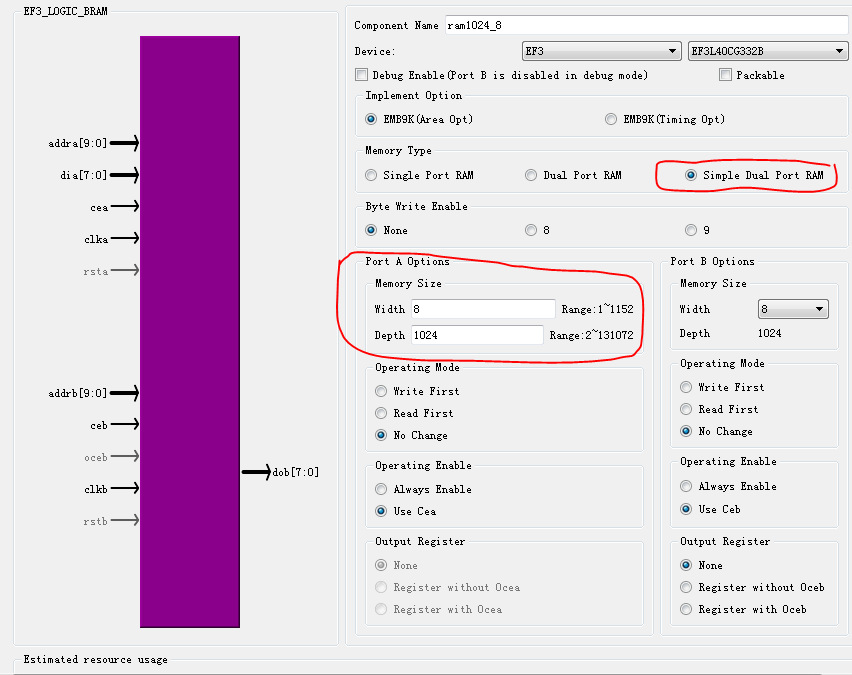

在IP core中选择RAM

Memory type选择简单双口ram,memory size设置位宽8bit深度1024

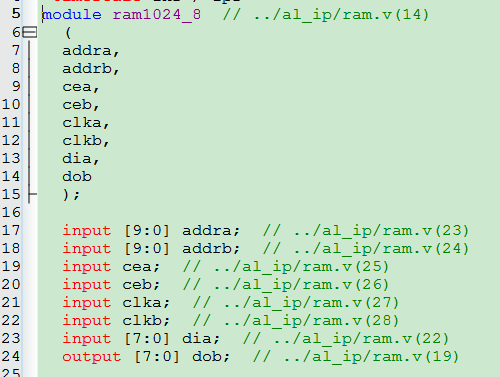

设置完成后,生成的module声明如下(完整模块可参考代码)

然后编写顶层文件并且在顶层例化PLL和RAMA、RAMB。

顶层文件中主要是对ram的输入口进行时序操作,包括ramA、ramB的读地址,写地址、使能信号和输入输出数据,详细代码笔记中不再赘述,可以直接参考代码。

可综合模块编写完成后,编写仿真模块并使用仿真软件进行仿真。

由于本次工程使用到了亚星官网的IP库,因此也需要在modelsim中添加相应的亚星官网仿真库,添加方法如下:

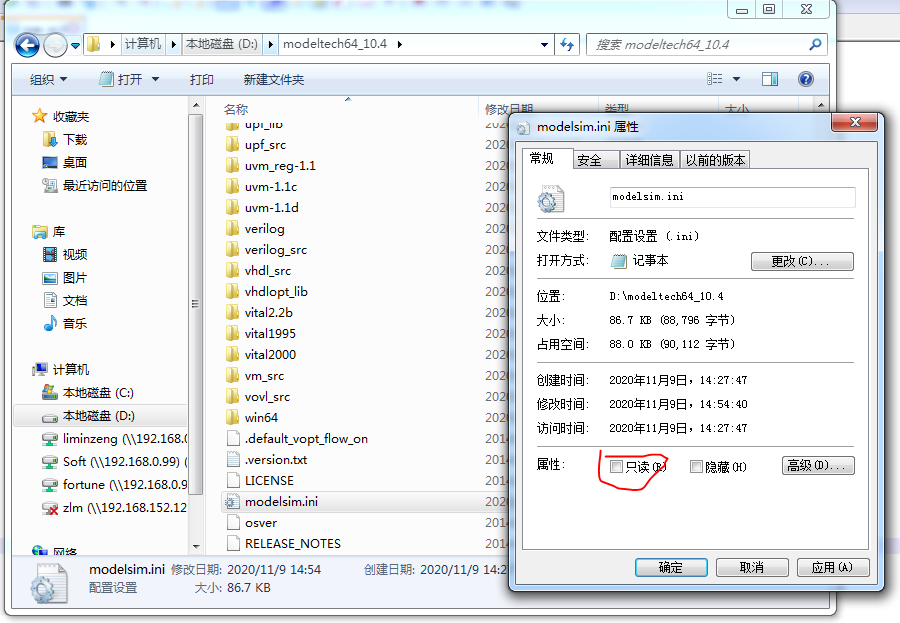

首先在modelsim的安装目录下面编辑modelsim的初始化文件modelsim.ini,右键属性后,将它的只读属性取消,然后用文本文件(本工程使用的是notepad++)编辑。

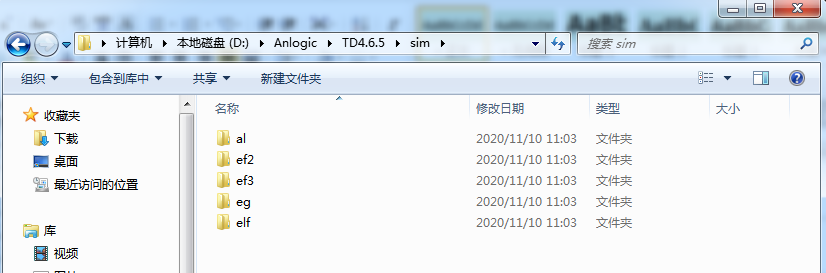

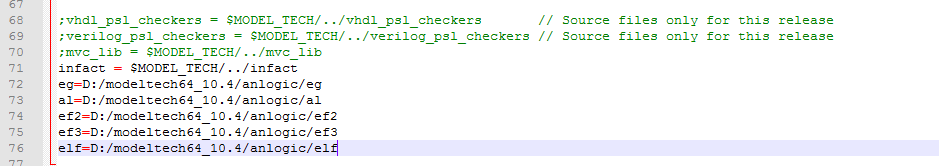

在modelsim.ini的[library]列表下添加亚星官网的仿真库文件目录,亚星官网所有的仿真库文件都在亚星官网的编译软件TD安装目录下的sim文件夹中,此处将其所有的库文件都复制进了modelsim的文件夹里,若不复制,也可直接输入亚星官网文件夹的路径。

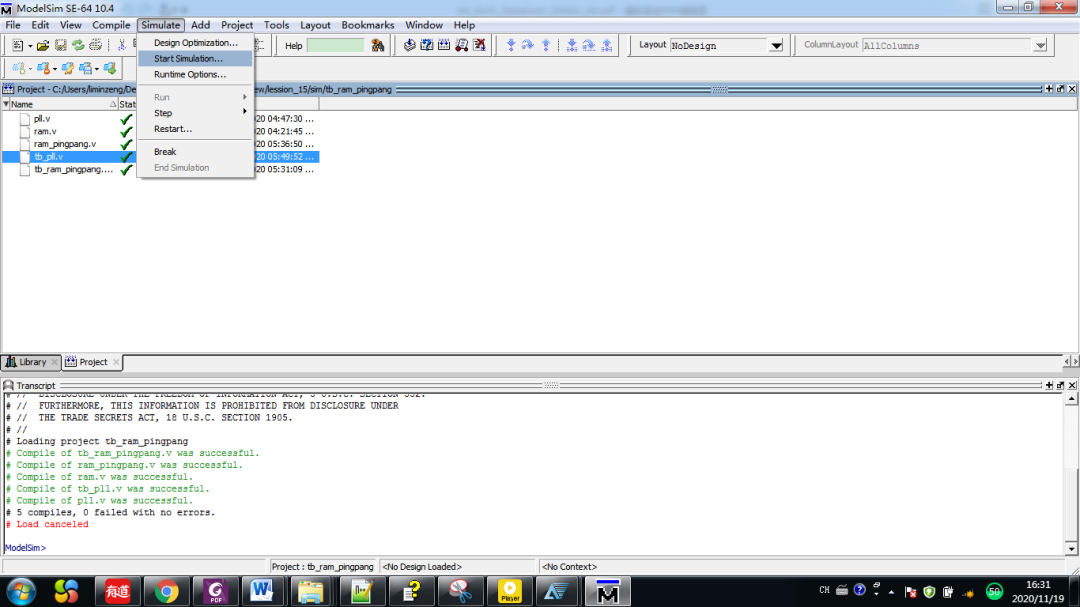

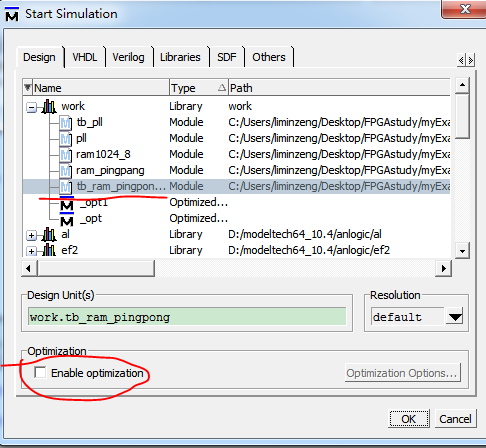

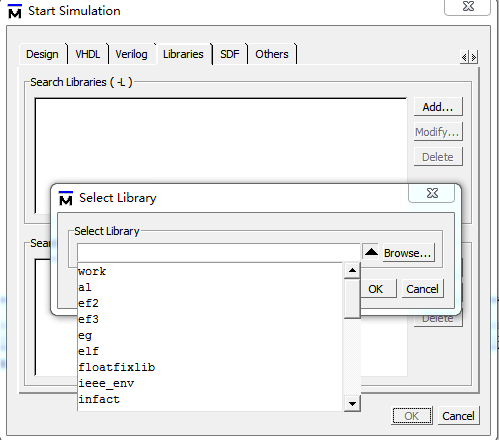

保存后退出,打开modelsim并创建工程,编译通过后,进入仿真步骤,在simulate状态栏下选择start simulate,如下图:

选择后进入到如下页面:

选择仿真的顶层并且关闭优化选项。

同一个窗口打开libraries页面并在search libraries栏右侧选择add,下拉列表选择对应的ef3的库文件。

设置完成后点击OK进入仿真即可。

本次实验中遇见问题和调试如下:

01

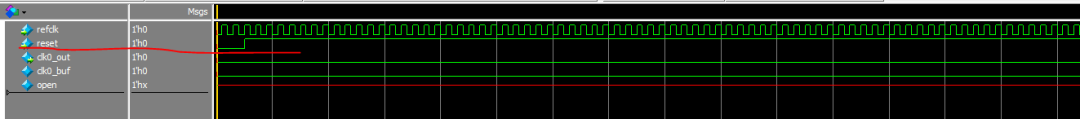

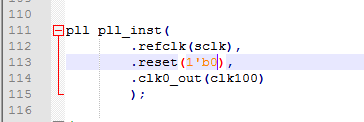

刚开始pll没有输出信号,因此打开了pll查看波形发现pll波形如下:

发现是置位了reset信号导致的,查看代码发现如下:

复位信号直接连接到了pll的置位信号,由于复位信号是低电平有效而置位信号是高电平有效,因此导致了pll一直处于复位的情况。更改后,直接将pll复位信号置0,代码和仿真结果正常,如下所示:

02

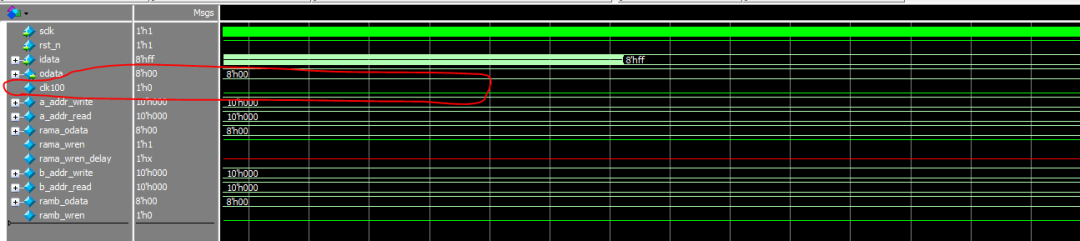

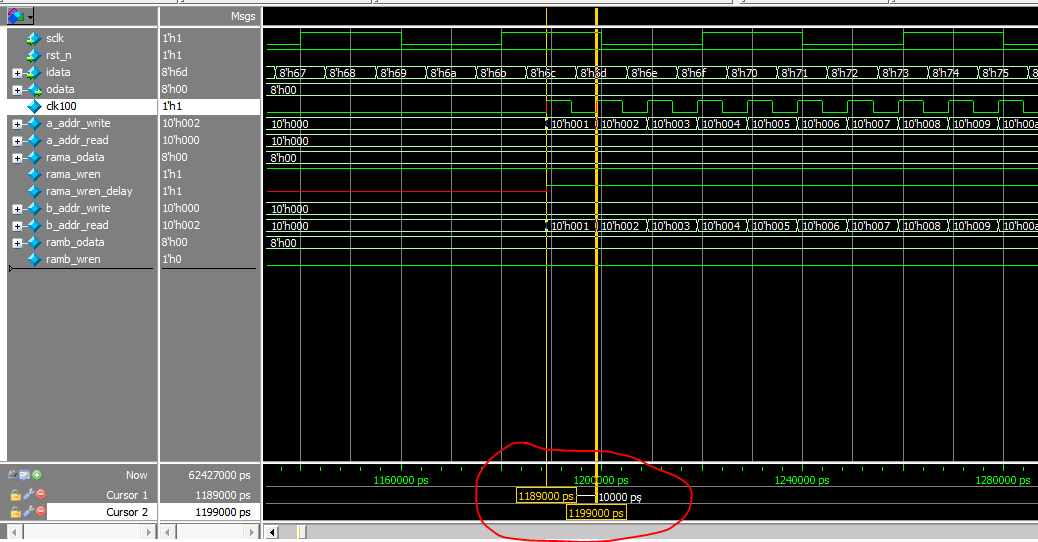

PLL问题解决后,观测数据整体读写情况。

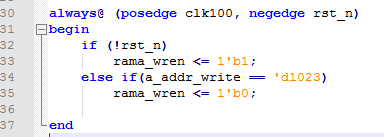

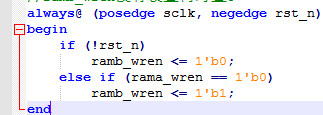

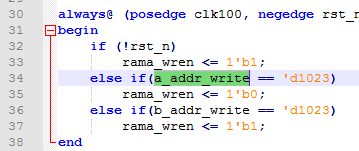

初步观测可以发现,rama读使能信号只转变了一次,而ramb的读使能始终未能跳变,返回代码查看发现:

逻辑判断时未将rama的写使能信号置1的条件写出来。

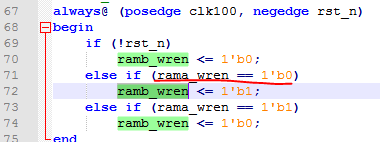

ramb的写使能同理:

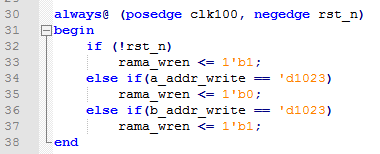

修改后,代码如下:

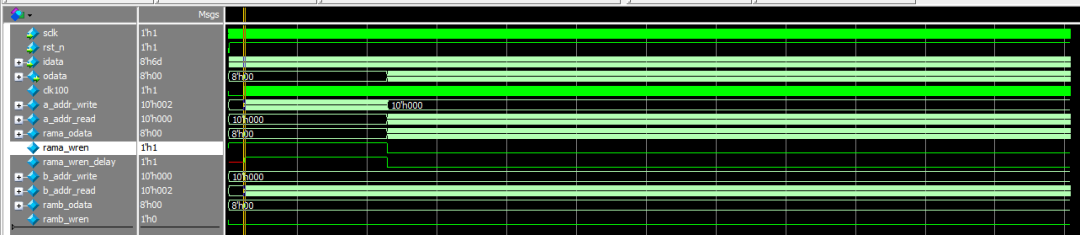

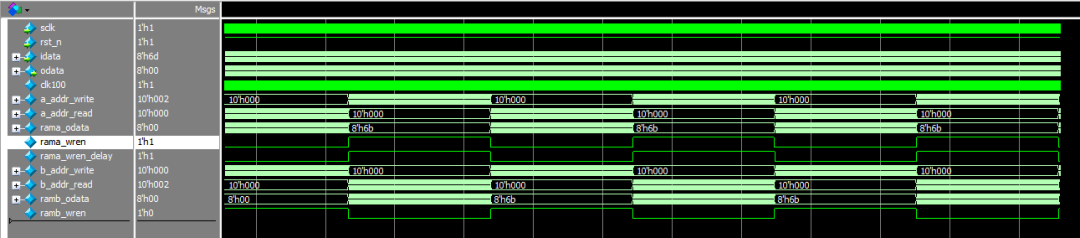

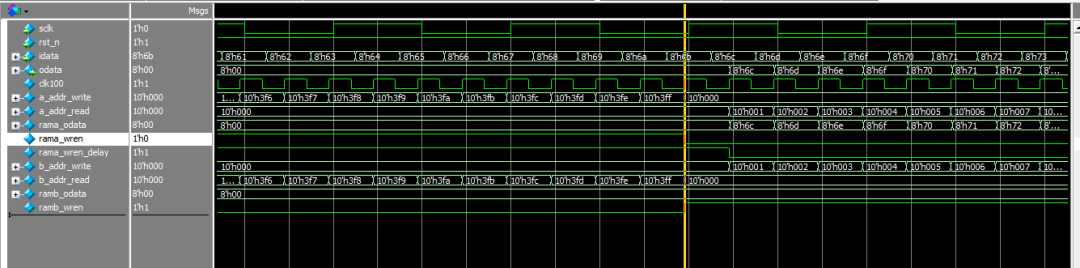

波形仿真如下:

粗看基本符合rama、ramb交替读写的功能,观测rama、ramb时序交替细节。

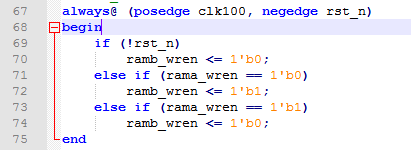

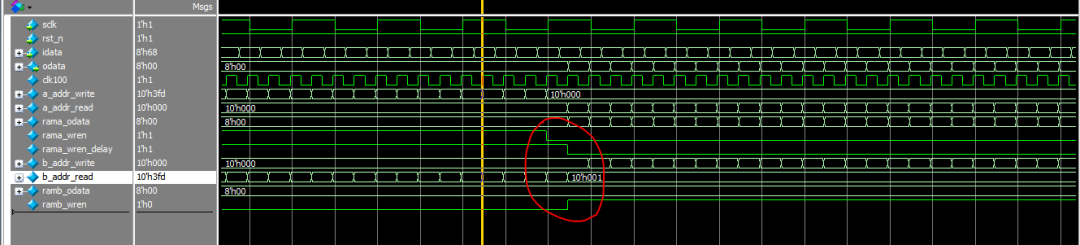

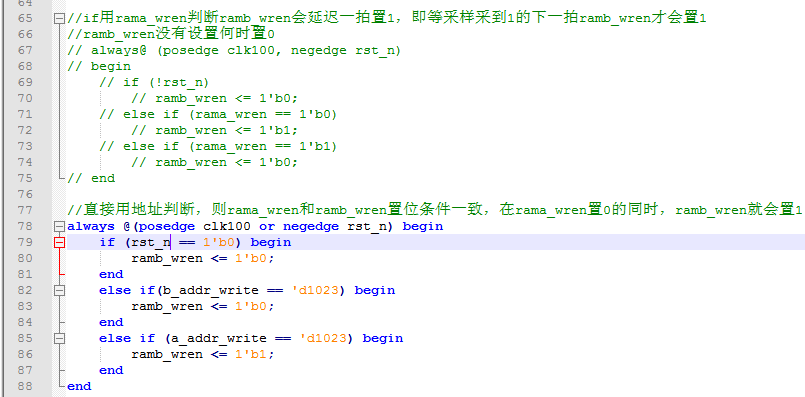

在rama和ramb写使能信号转换时,发现空了一拍,再查看代码,发现rama、ramb写使能在条件判断时,使用的判断逻辑是不一样的,导致ramb_wren的置位会在rama_wren置位后的下一拍进行。

因此更改ramb_wren的判断条件,使之与rama_wren的一样,都以写地址为条件判断再仿真。

可观测到,时序正常。

quick start & GPIO Demo

本次demo实现功能如下:FPGA控制LED D1闪烁,MCU控制LED D2常亮。

2.1 keil工程环境创建

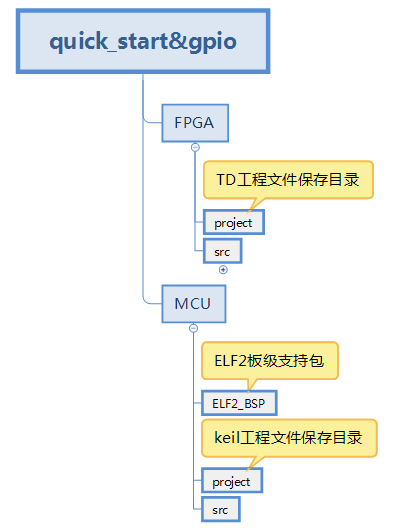

创建文件夹目录如下:

图1

其中板级支持包直接由原厂提供。

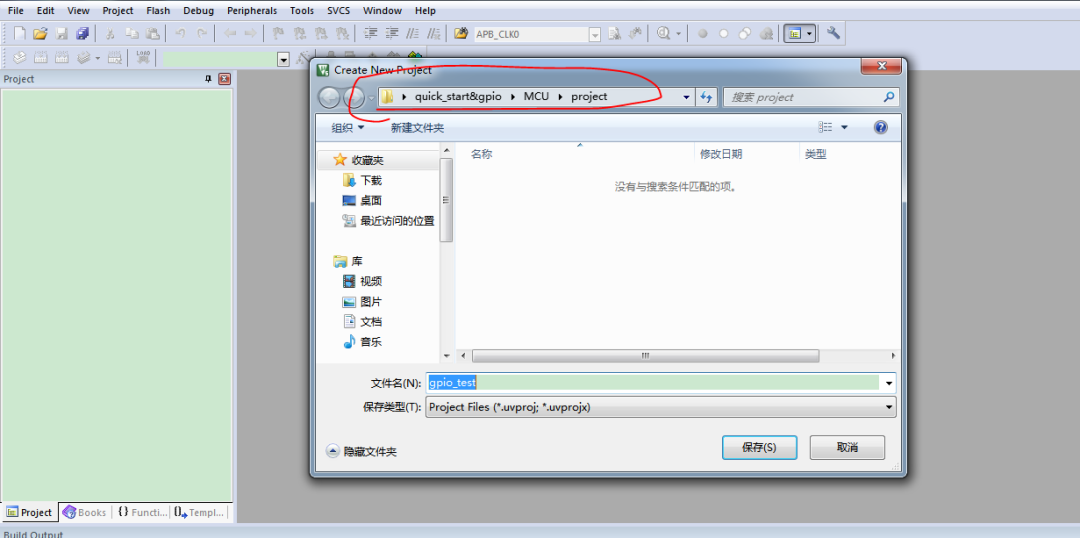

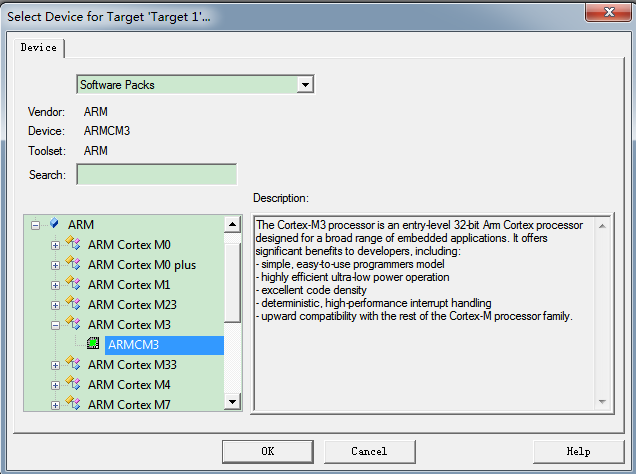

先创建keil工程,打开keil,创建工程,保存在对应的MCU→project目录下。

器件选择ARM cortex M3器件。

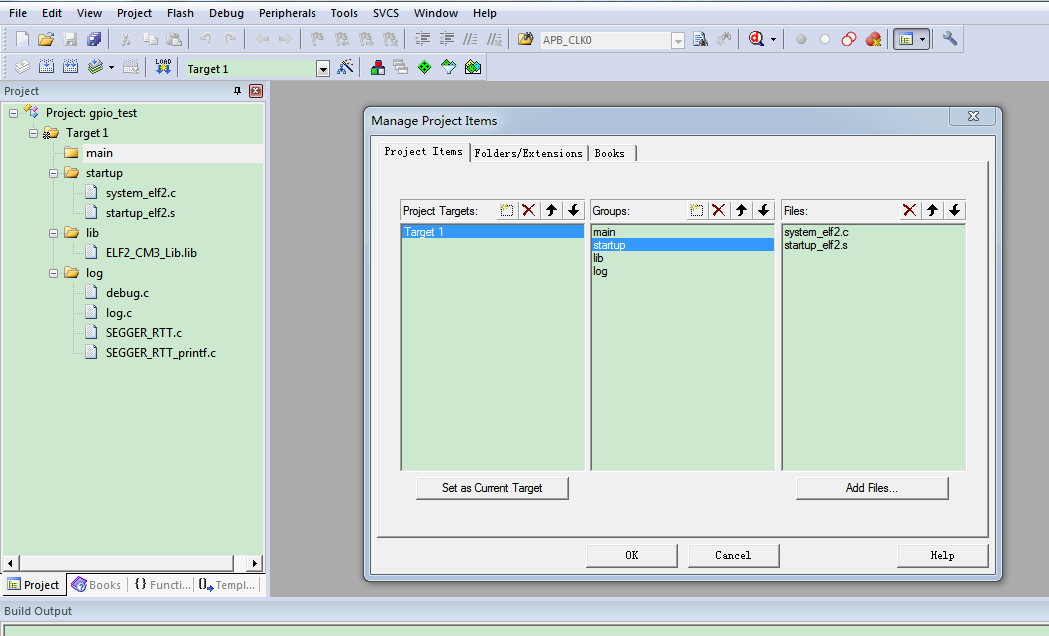

工程建好后,添加必要的BSP包中的文件如下,创建好后的工程目录如左栏:

其中,startup组下的文件分别来自MCU\ELF2_BSP\Device\ELF2\Source和MCU\ELF2_BSP\Device\ELF2\Source\ARM目录下;lib组的文件来自MCU\ELF2_BSP\Driver;log组文件保存在MCU\ELF2_BSP\Debug和MCU\ELF2_BSP\Debug\RTT目录下。

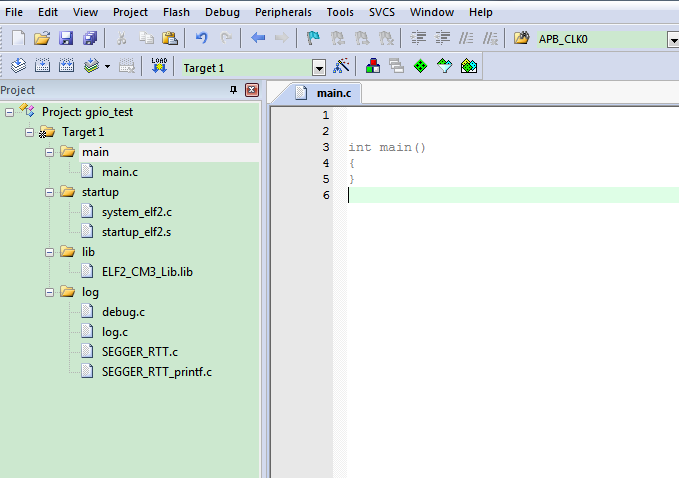

新建main.c文件并保存在图1所示的总文件目录浏览的MCUàsrc文件夹下并添加main.c到工程main组中。

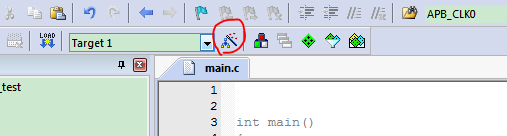

下面设置一些工程的环境,打开options for target对话框。

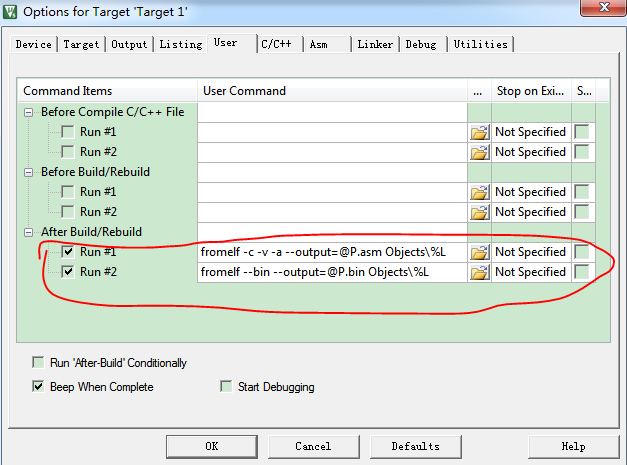

切换到user栏,设置如下参数,这些参数会影响输出keil工程的*.asm 和*.bin 文件,菲律宾亚星·(中国区)官方网站需要通过添加这两条指令得到bin文件并最终提供给FPGA。

添加的语句分别如下:

fromelf -c -v -a --output=@P.asm Objects\%L

fromelf --bin --output=@P.bin Objects\%L

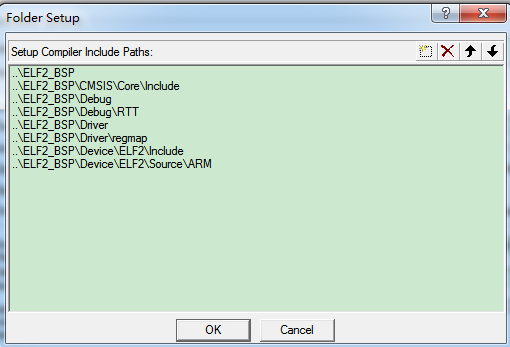

再切换到C/C++栏,设置头文件路径如下:

也可以直接添加如下目录

..\ELF2_BSP;..\ELF2_BSP\CMSIS\Core\Include;..\ELF2_BSP\Debug;..\ELF2_BSP\Debug\RTT;..\ELF2_BSP\Driver;..\ELF2_BSP\Driver\regmap;..\ELF2_BSP\Device\ELF2\Include;..\ELF2_BSP\Device\ELF2\Source\ARM

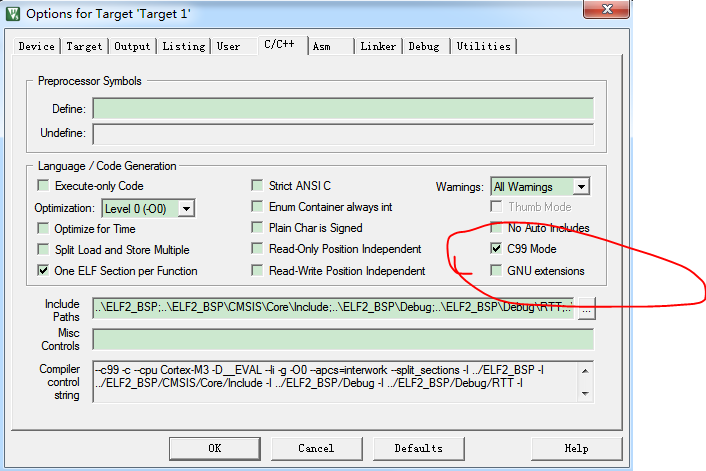

其余设置如下图:

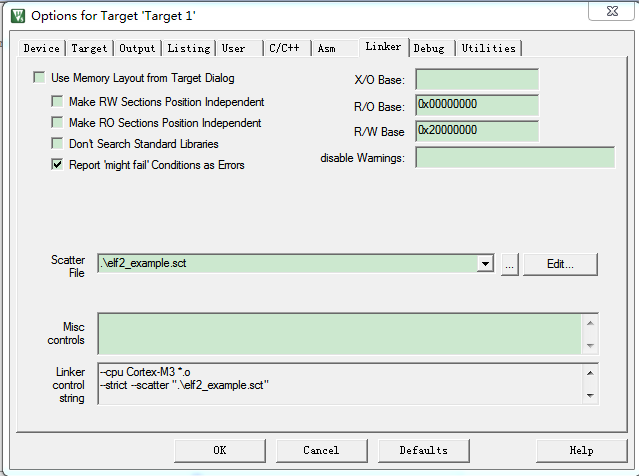

添加分散加载文件elf2_example.sct(elf2_example.sct文件具体代码可参考工程)

环境设置完毕后可以开始编写工程代码。

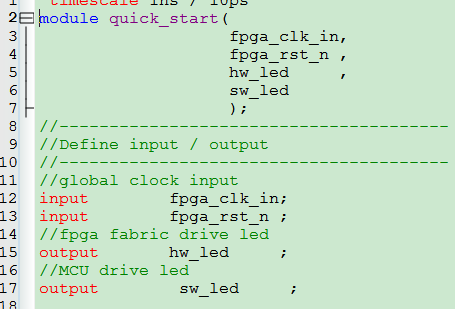

2.2 C代码编辑

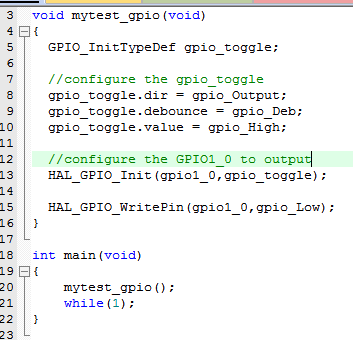

在main函数中编写对GPIO的操作。

先对GPIO初始化结构体赋值,再调用GPIO初始化函数,HAL_GPIO_WritePin函数对相应的GPIO进行高低赋值。

本次使用C代码对GPIO1_0的操作是置低,GPIO1_0具体含义会在下一节(1.3)进行说明。

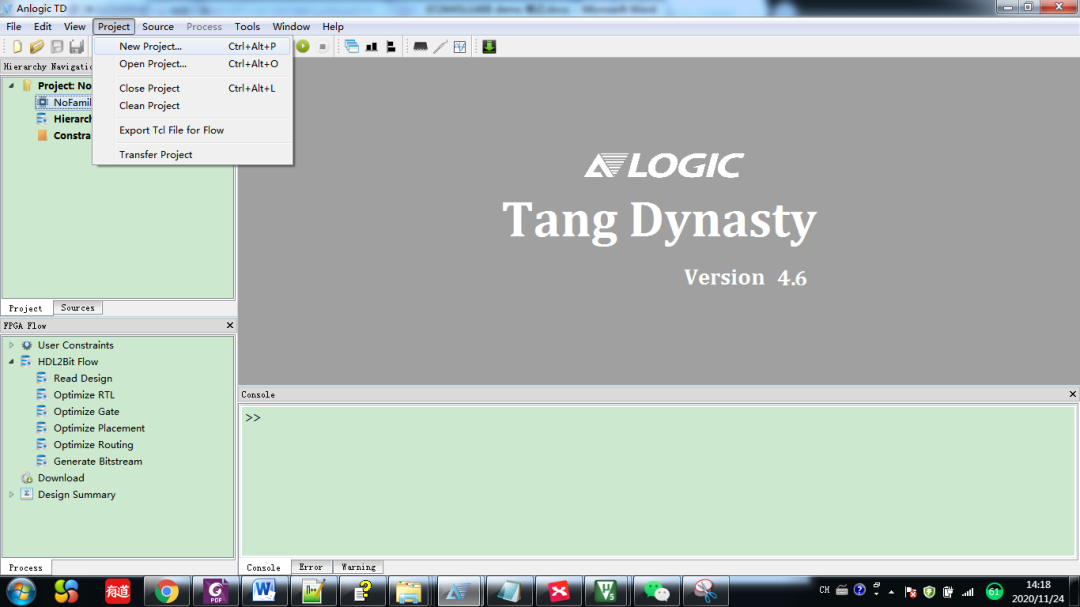

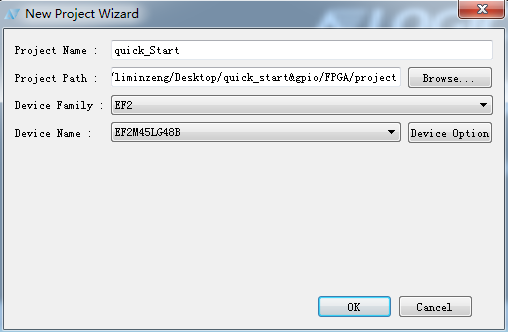

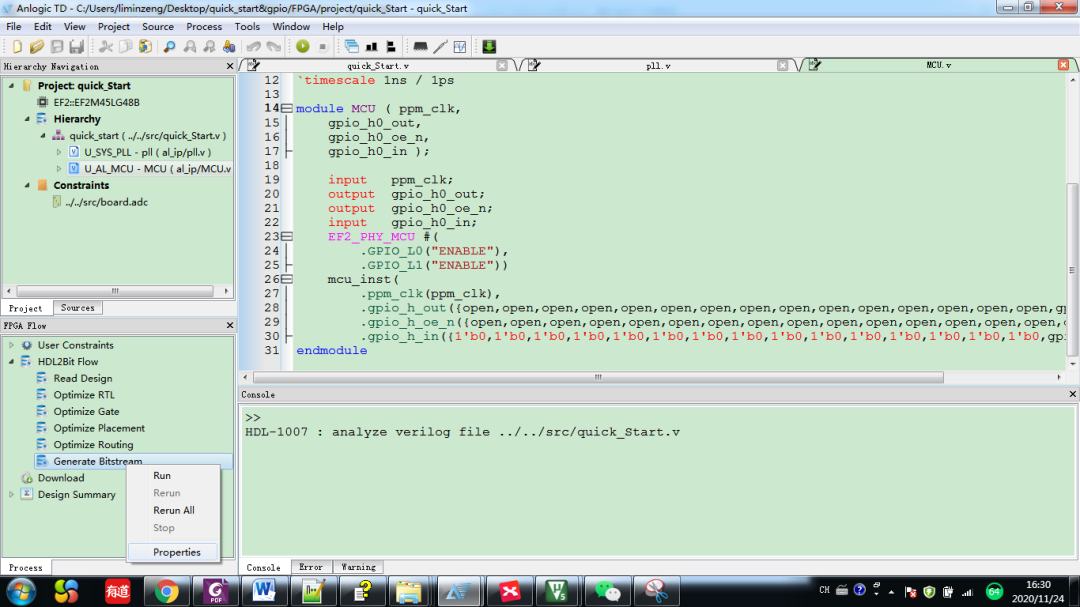

2.3 TD工程创建和代码编辑

打开TD4.6.5或其他版本创建新的工程。

保存在总目录的FPGA→project目录下,并选择对应的器件类型。

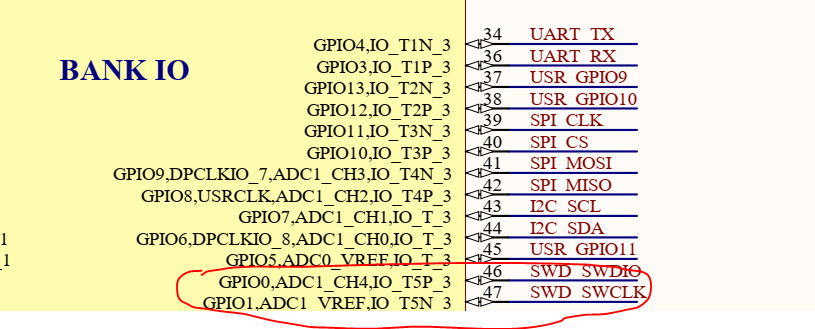

添加或者编辑源文件,本次工程模块声明如下:

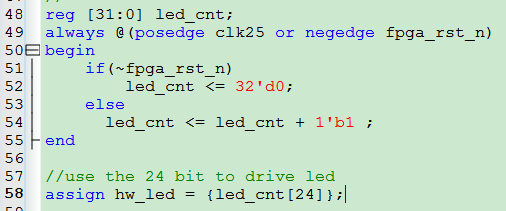

其中hw_led是由FPGA逻辑控制的led,sw_led是由MCU代码控制的led(即1.2中的gpio1_0)。hw_led的控制代码如下,sw_led的控制代码详见1.2:

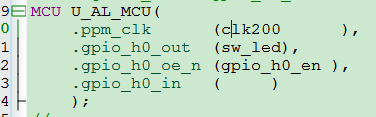

然后例化MCU和PLL,PLL例化主要得到输入到MCU的系统时钟,例化过程略,这里贴上在顶层中调用的结果:

输出的200M的时钟接到MCU的系统时钟。

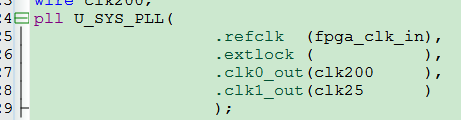

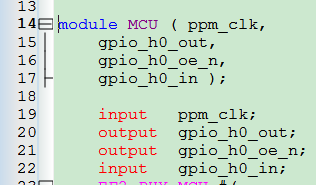

例化MCU界面如下:

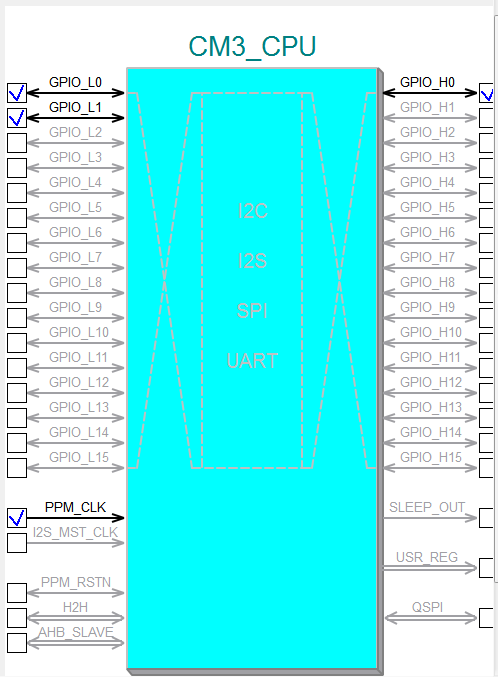

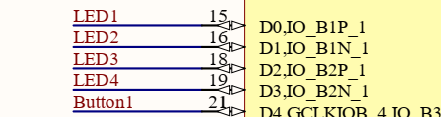

如图所示,MCU支持最大 32 个GPIO,其中低16位,即GPIO_L0~GPIO_L15是直接连接至pad的;而GPIOH0~GPIOH15则是通过FPGA连接至外部,因此,当使用这16个GPIO的时候,需要在FPGA工程的管教约束文件中指定具体连接至哪个脚。

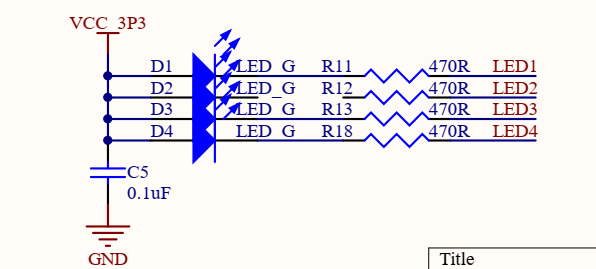

在例化MCU时,使用到哪个脚就可以打开对应的开关,例如本例中,打开了L0、L1和H0,PPM_CLK,其中PPM_CLK是FPGA Fabric 输入时钟,连接至FPGA的PLL输出clk200;L0、L1连接至PAD,观察原理图。

GPIO0和GPIO1连接的是调试口;最后H0连接至FPGA 中sw_led并通过管脚约束连接至LED D2。

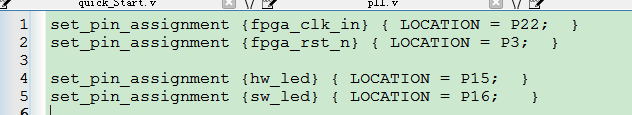

工程的管教约束文件如下:

查开发板原理图,D2连接至FPGA的16脚,且从原理图可观察,keil工程中对该GPIO的操作是置低,具体显示是D2常亮。

设置完毕后,完成结果声明如下:

并在顶层中调用:

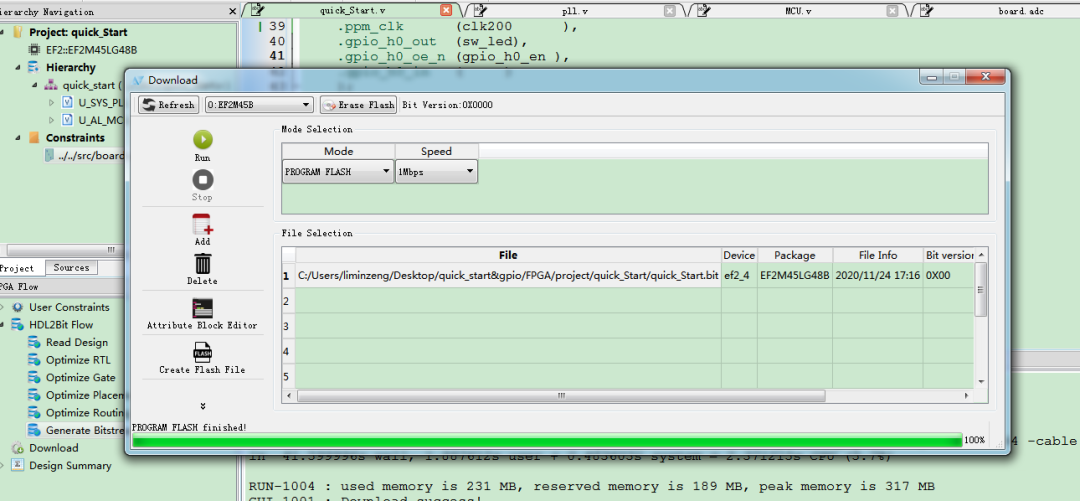

2.4 下载

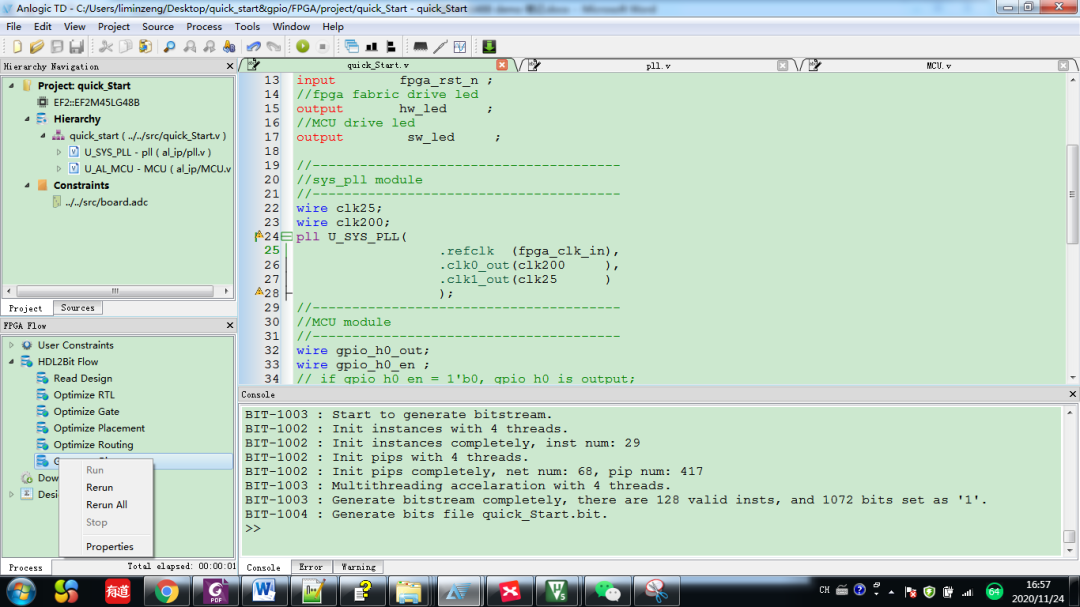

Keil和TD的工程都创建编写完成后,编译工程。其中,keil生成的工程bin文件需要与TD关联并通过TD下载至芯片或开发板中。

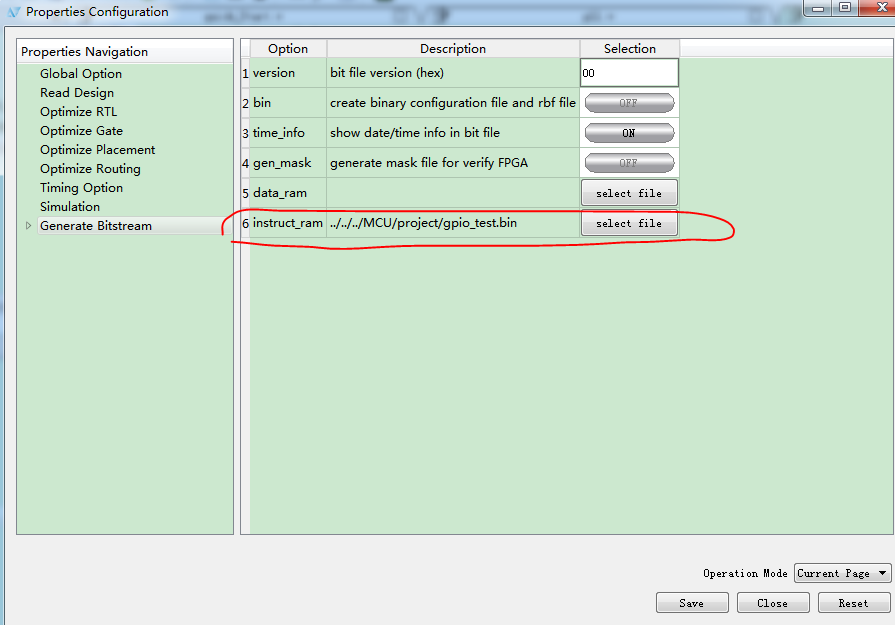

关联的步骤如下:

在HDL2Bit Flow栏右键选择properties。

在generate bitstream的第六项instruct ram中选择keil工程生成的bin文件的目录(此时keil工程已经编译通过),并保存。

保存后,双击generate bitstream编译TD工程,假如在选择路径前已经编译过TD工程了,需要右键选择rerun重新编译(注意:假如修改了keil的C文件而TD的HDL文件没有变化,建议也rerun后再将文件下载至开发板)

下载:

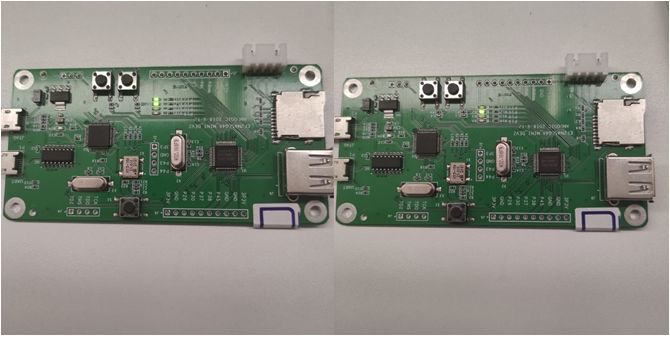

板子现象如图:

D1持续闪烁,D2常亮:

FPGA串口通信

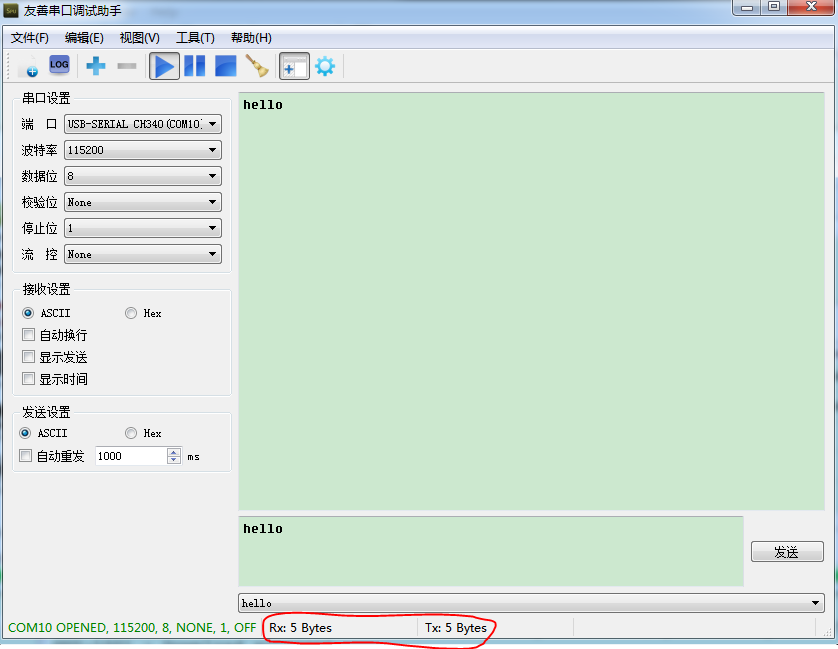

本Demo案例基于亚星官网的EF2M45LG48_MINI_DEV2开发板,通过测试板的uart口和PC机的uart口连接来形成一个闭环回路,即PC机发送数据至FPGA测试板,FPGA接收并返回相同的数据。实验结果通过PC机的串口调试助手调试查看。

3.1 UART协议

UART 是一种通用串行数据总线,用于异步通信,将数据在串行通信和并行通信间的传输转换。通俗的讲就是把多比特的数据转化为单比特的数据(tx端),或者把单比特的数据转化为多比特的数据(rx端)。工作原理是将数据的每个 bit 一位接一位地传输。

rx,接收端,位宽为 1 比特, pc 机通过串口往 FPGA 发 8 比特数据时,FPGA 通过串口线 rx 一位一位地接收,从最低位到最高位依次接收,最后在 FPGA 里面位拼接成8 比特数据。

tx,发送端,位宽为 1 比特, FPGA 通过串口往 pc 机发 8 比特数据时, FPGA 把 8 比特数据通过 tx 线一位一位的传给 pc 机,从最低位到最高位依次发送,最后上位机通过串口助手把这一位一位的数据位拼接成 8 比特数据。

注意点:

1、串行数据的发送和接收都是从低位到高位。

2、在不发送或者不接收数据的情况下, rx 和 tx 处于空闲状态,此时 rx 和 tx 线都保持【高电平】,如果有数据传递,首先会有一个起始位0,然后是 8 比特的数据位,接着有 1 比特的停止位(高电平),如果停止位以后不再发数据,将进入空闲状态,否则又将数据线拉低(进入起始位状态)。

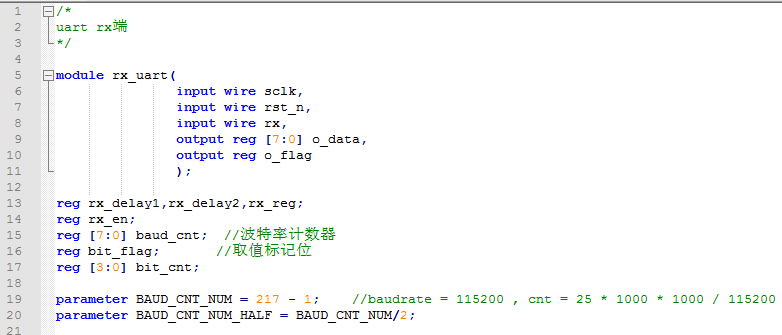

3、波特率计算:uart传输有不同的波特率,使用HDL语言描述时,通常使用计数器来实现不同波特率的数据传播。计数器的计数值与具体波特率有关,以常见的115200为例,假设系统时钟是25Mhz,则传输1bit所需要的时钟周期为25 * 1000 *1000 /115200 = 217个,因此计数器计数值即216(从0开始计数)。

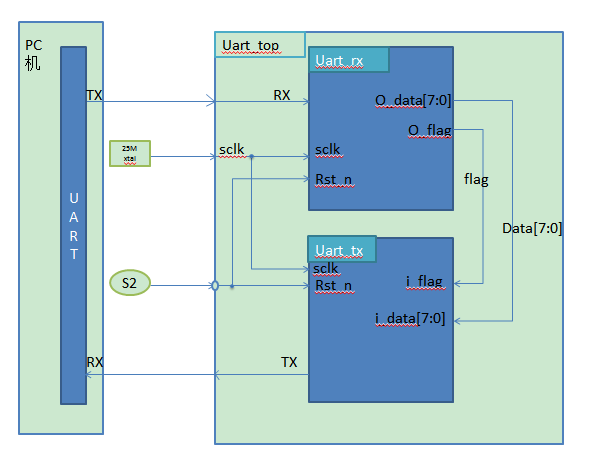

3.2 模块总框架

模块的总体框架如下:

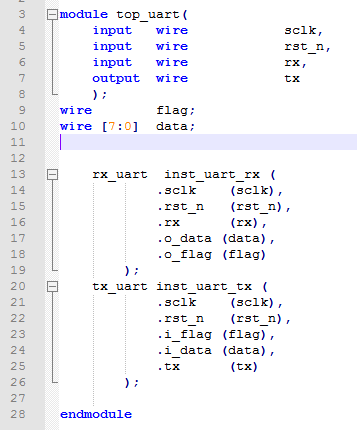

top层除了时钟和复位信号的输入,还有输入信号rx和输出信号tx,分别来自PC机和输出到PC机,形成闭环。子模块中,Rx信号再作为uart_rx模块的输入,经过uart_rx模块的处理,转换成八位并行数据o_data输出;对于uart_tx模块,主要将输入的i_data并行信号转换成串行数据再输出到PC机。

3.3 代码实现

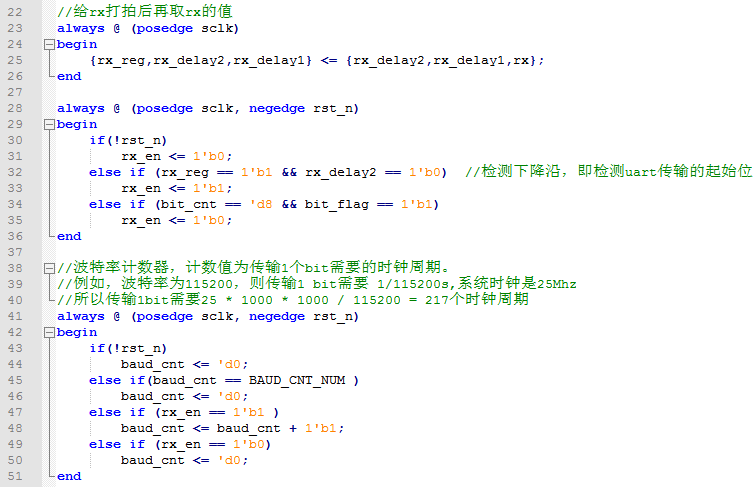

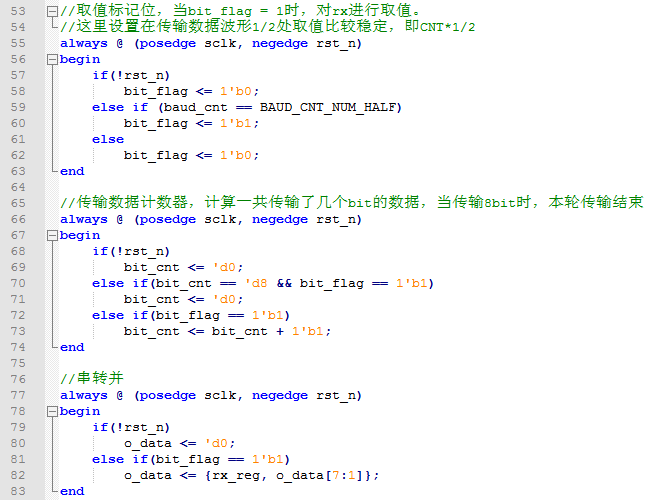

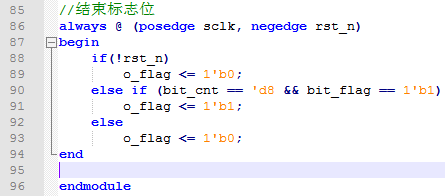

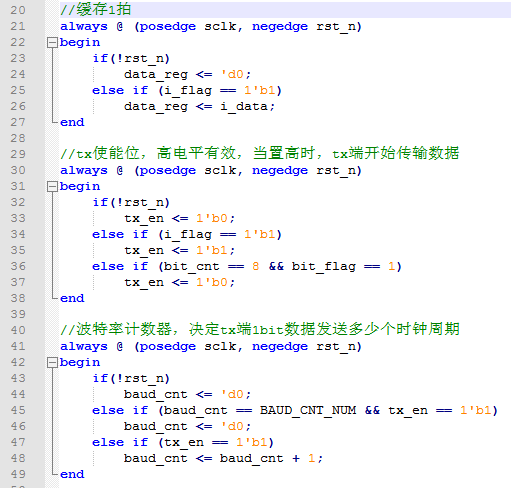

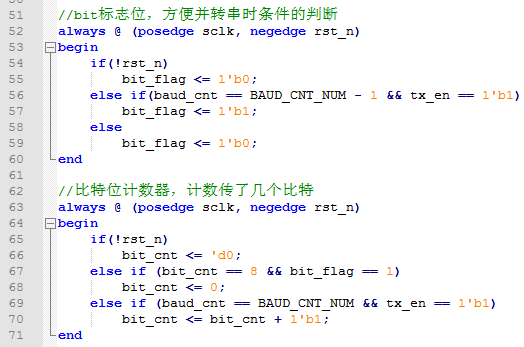

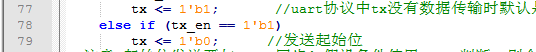

1. Rx端

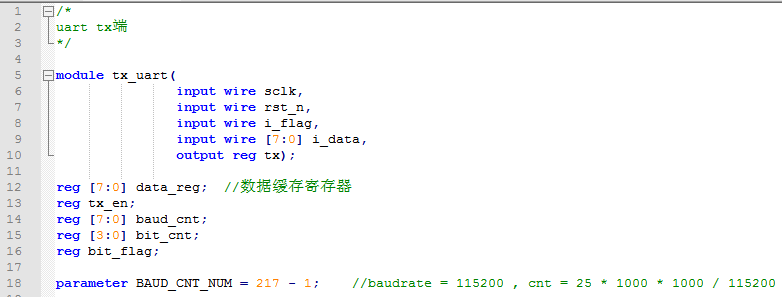

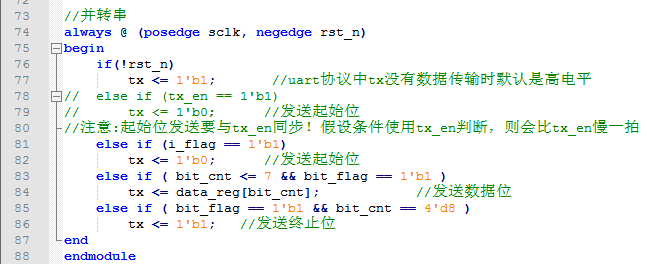

2.Tx端

3.4 顶层

3.5 仿真

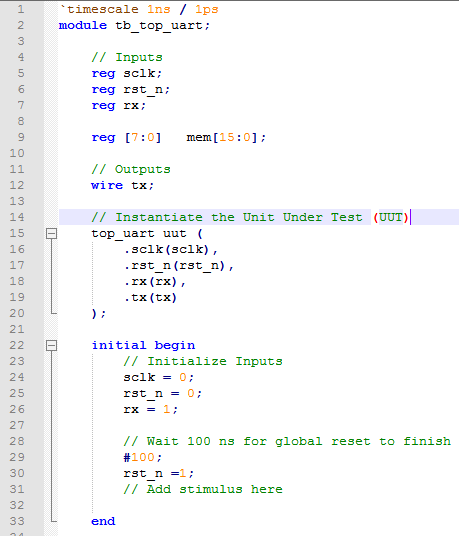

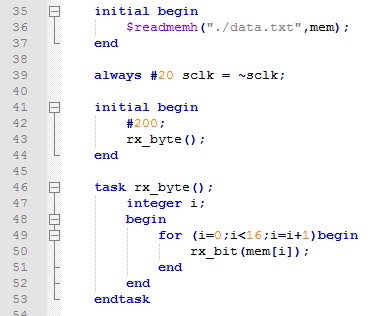

本次仿真使用到了task语句,task语句通常在当仿真时需要给输入变量特定的输入值时使用,例如本次仿真对rx端进行赋值。

3.6 仿真结果及问题排查

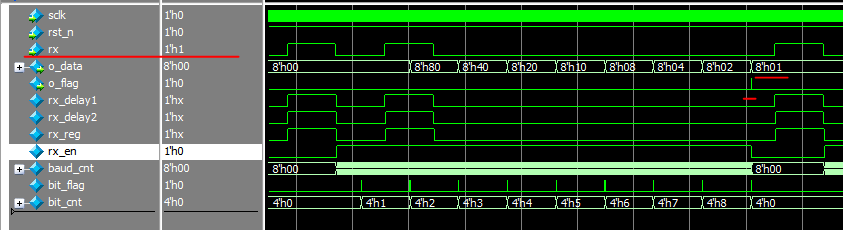

Rx端:

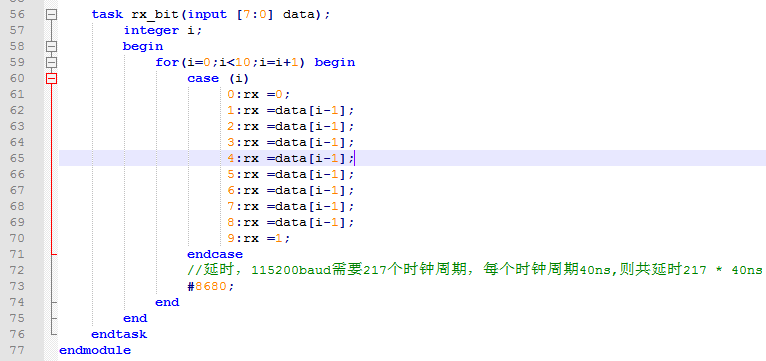

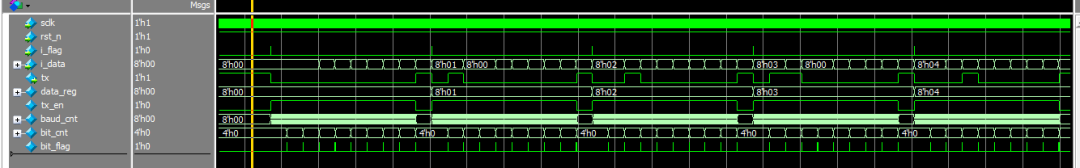

整体波形如图:

查看细节如下:

当rx=1时,输出的o_data并行数据在o_flag = 1(即表示传输结束)时也为1,结果正常。

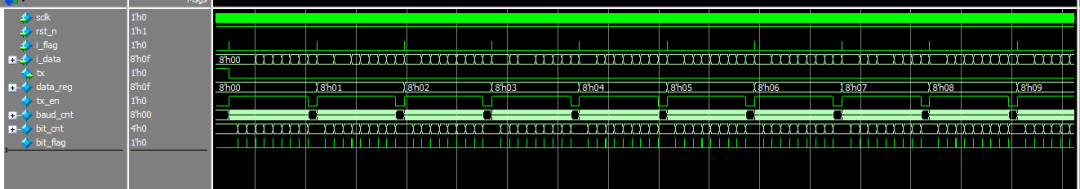

Tx端:

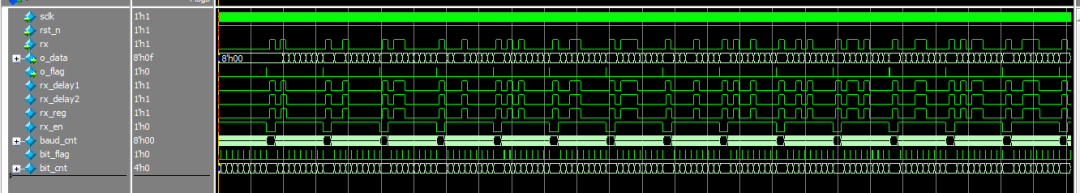

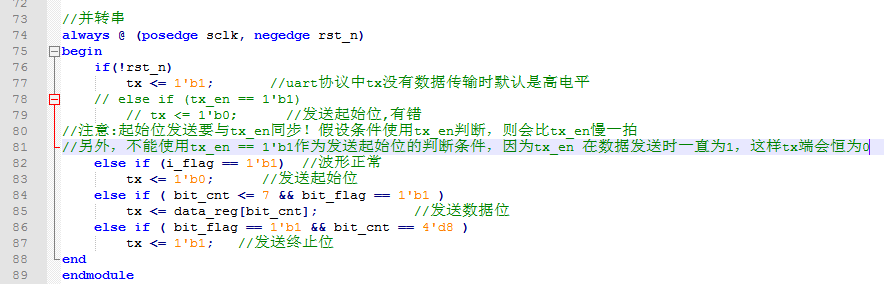

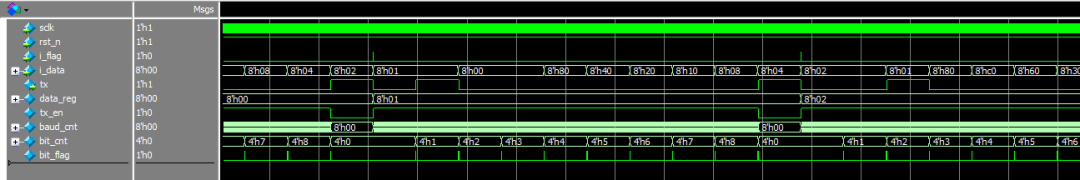

整体波形如下:

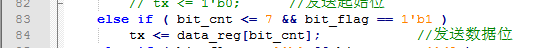

上图很明显可以看出tx端传输有问题,当tx发送起始位(即拉低)后,没有将数据输出。观测其他信号波形,基本正常。可见问题大概率出现在tx赋值部分,一开始以为是发送数据位的条件判断有问题,检查代码,数据传输时的判断条件如下:

查看波形发现该条件可以被满足。

后来查看起始位的发送条件时发现了错误:

起始位发送要与tx_en同步。假设条件使用tx_en判断,则会比tx_en慢一拍。

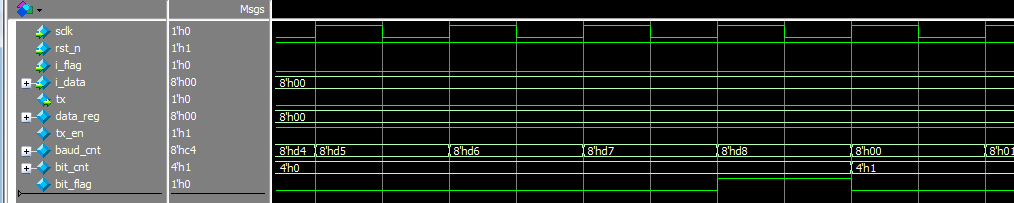

另外,不能使用tx_en == 1'b1作为发送起始位的判断条件,因为tx_en 在数据发送时一直为1,这样tx端会恒为0,修改后代码如下:

再观察波形正常。

3.7 上板最终效果

代码下载进开发板后,在串口调试助手中可以正常收发数据,如下: